2024年7月10日

# 最先端 ロジックトランジスタ技術 研究開発動向(基礎と応用)

産業技術総合研究所 先端半導体研究センター 八木下 淳史

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

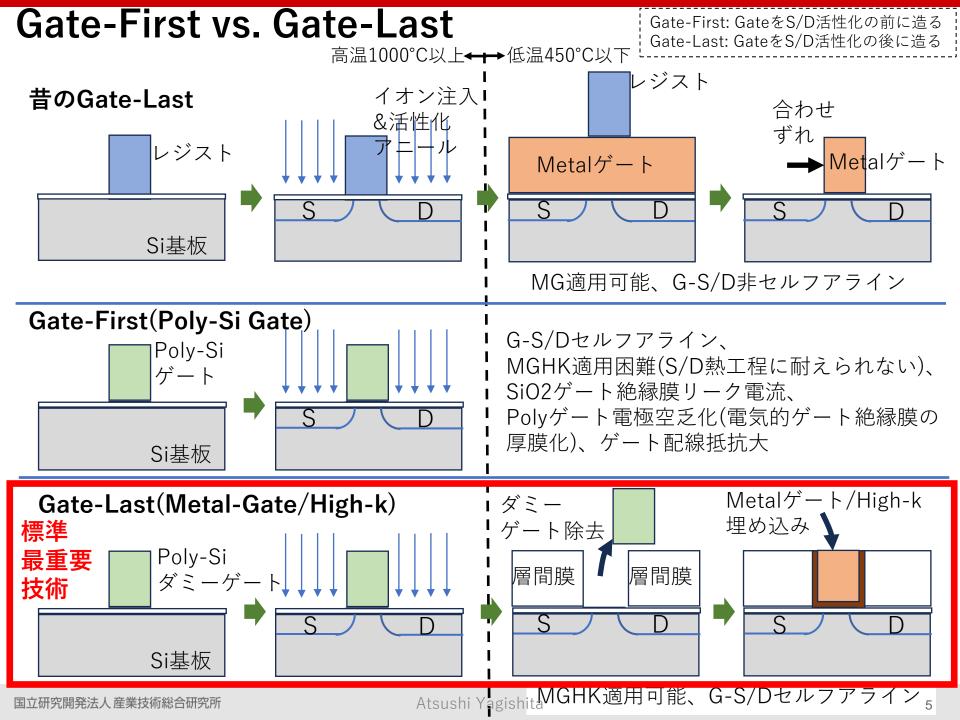

- (2)Gate-First, Gate-Lastプロセス比較

- (3)PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

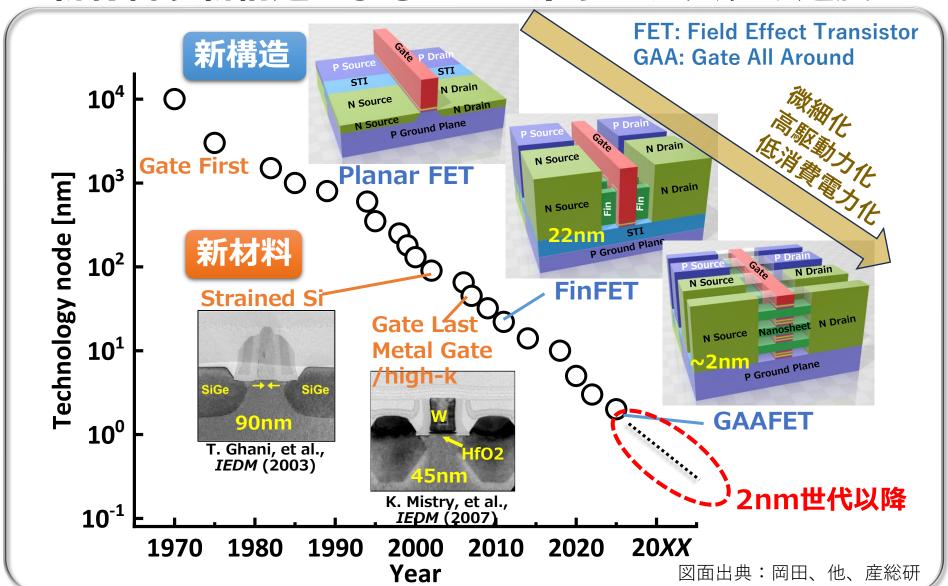

#### 新材料や新構造によるCMOSトランジスタの進展

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

- (2)Gate-First, Gate-Lastプロセス比較

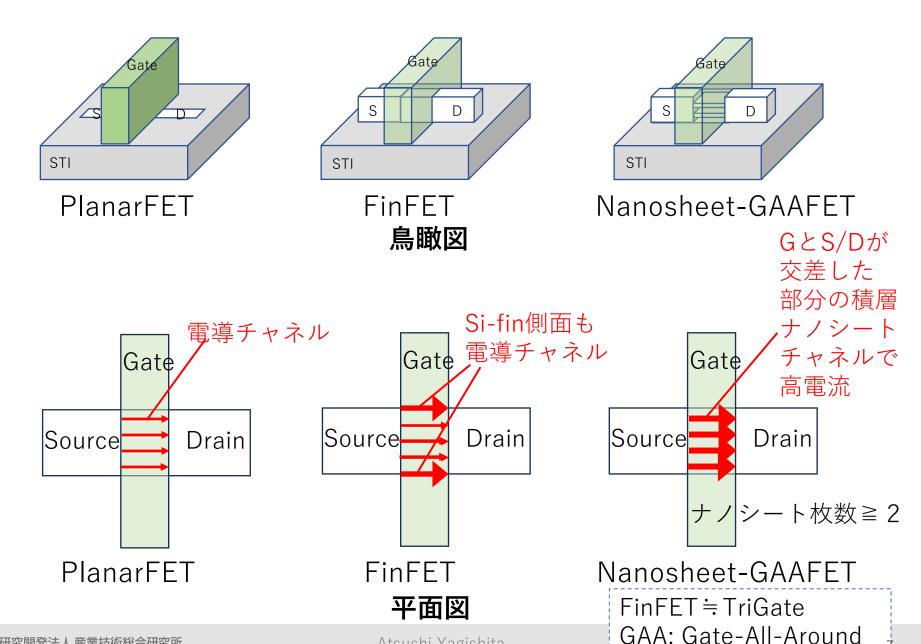

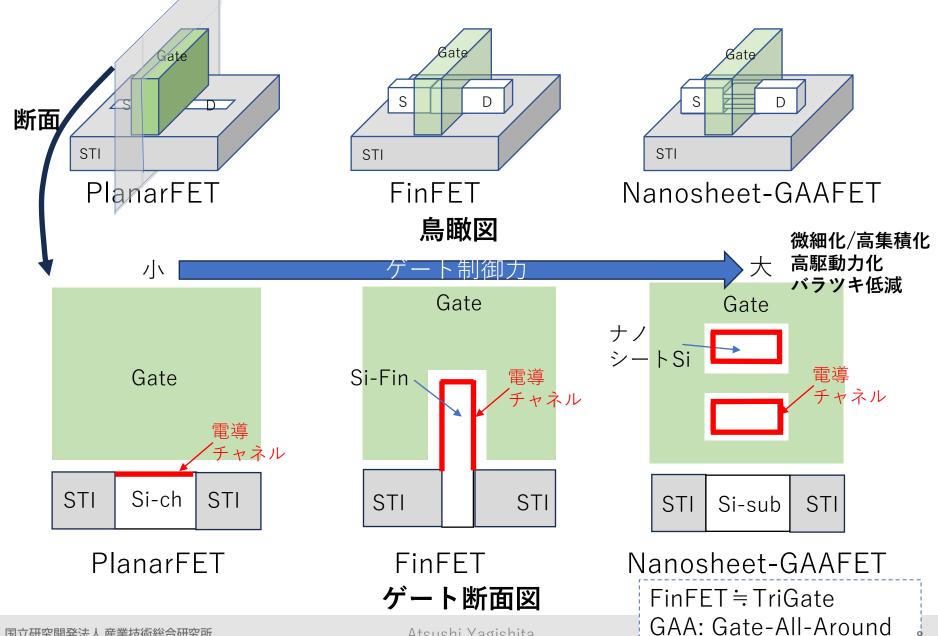

- (3)PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

- (2)Gate-First, Gate-Lastプロセス比較

- (3) PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

#### Planar FET, FinFET, GAAFETの比較

#### Planar FET, FinFET, GAAFETの比較

国立研究開発法人產業技術総合研究所

Atsushi Yagishita

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

- (2)Gate-First, Gate-Lastプロセス比較

- (3)PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

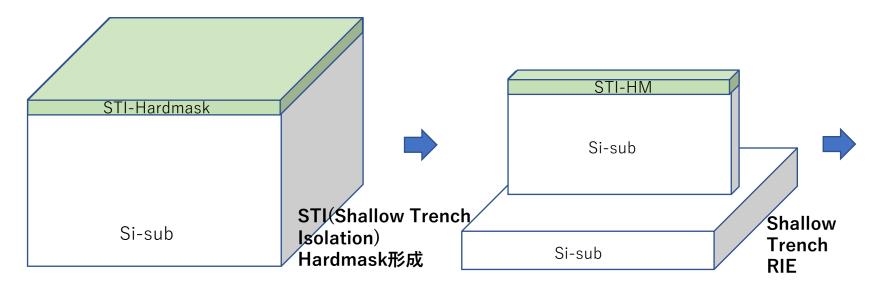

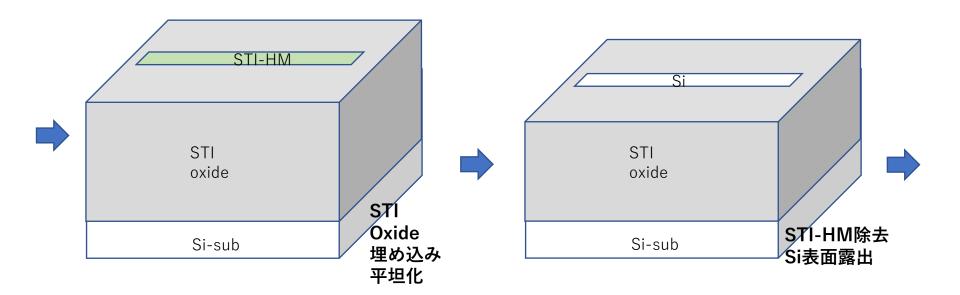

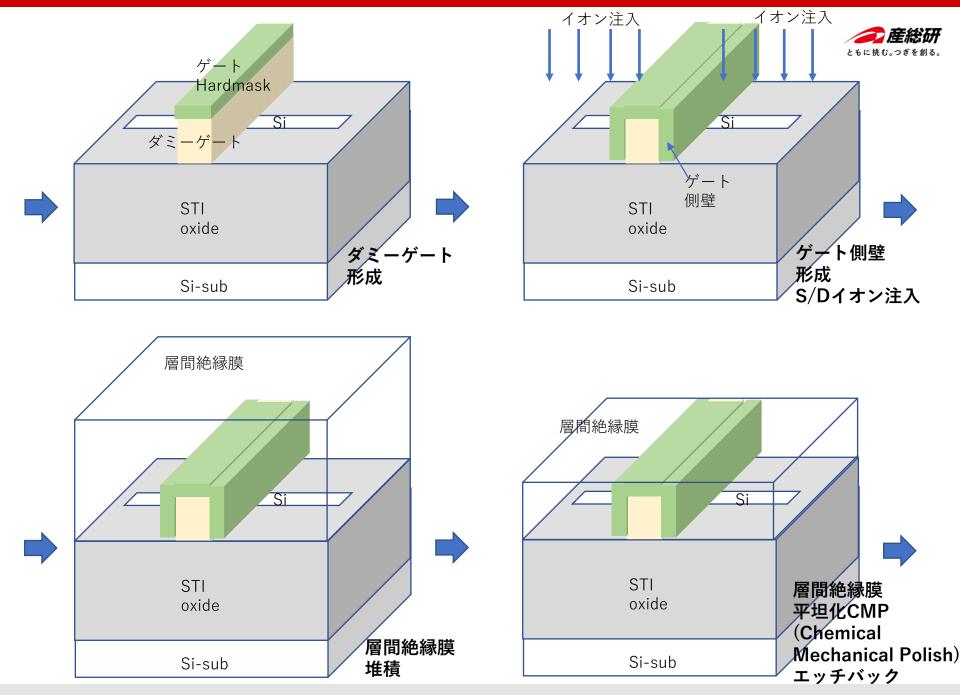

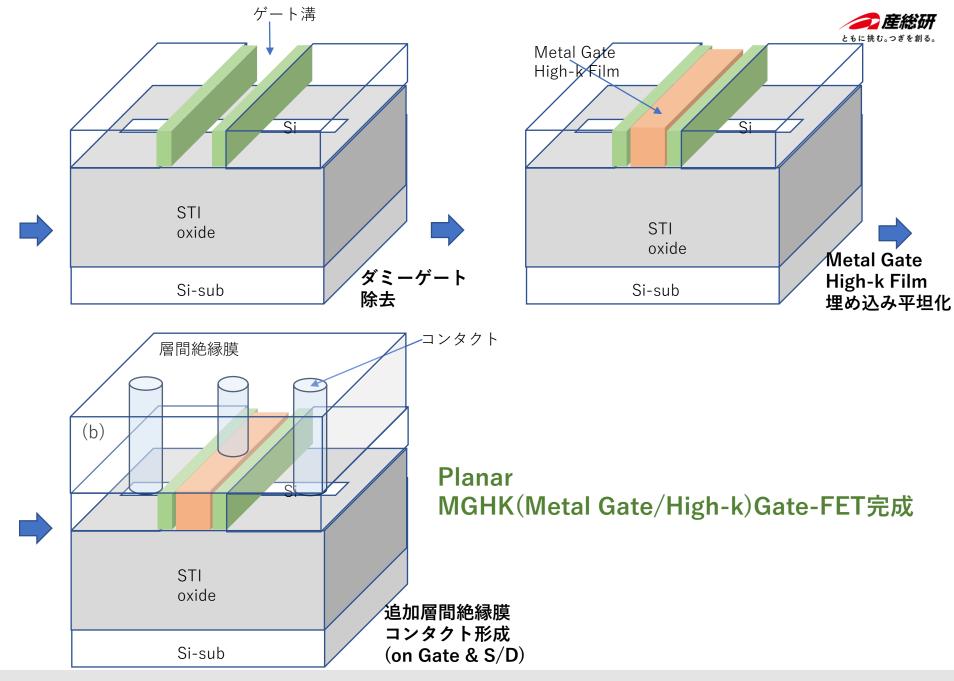

#### Planar-FETプロセスフロー鳥瞰図

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

- (2)Gate-First, Gate-Lastプロセス比較

- (3) PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

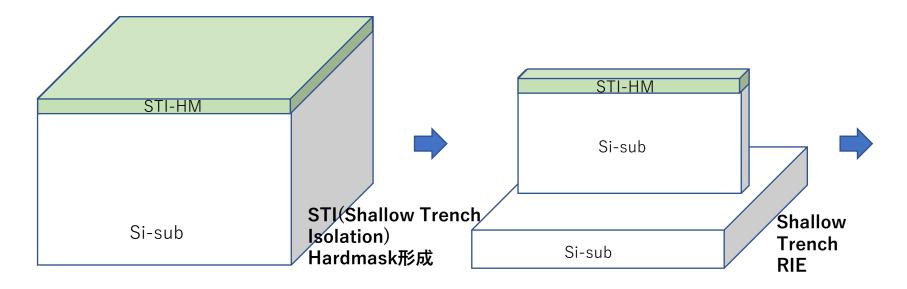

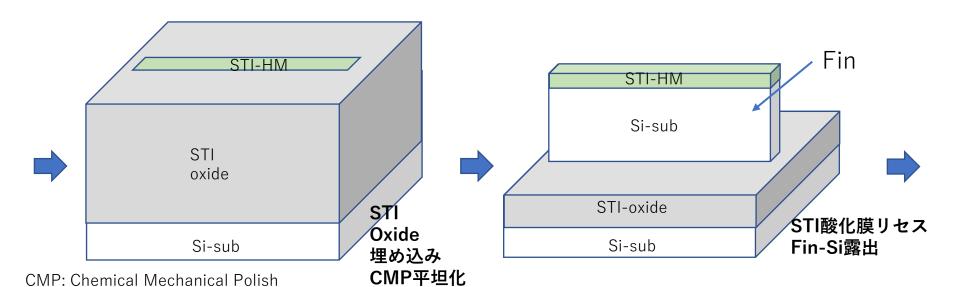

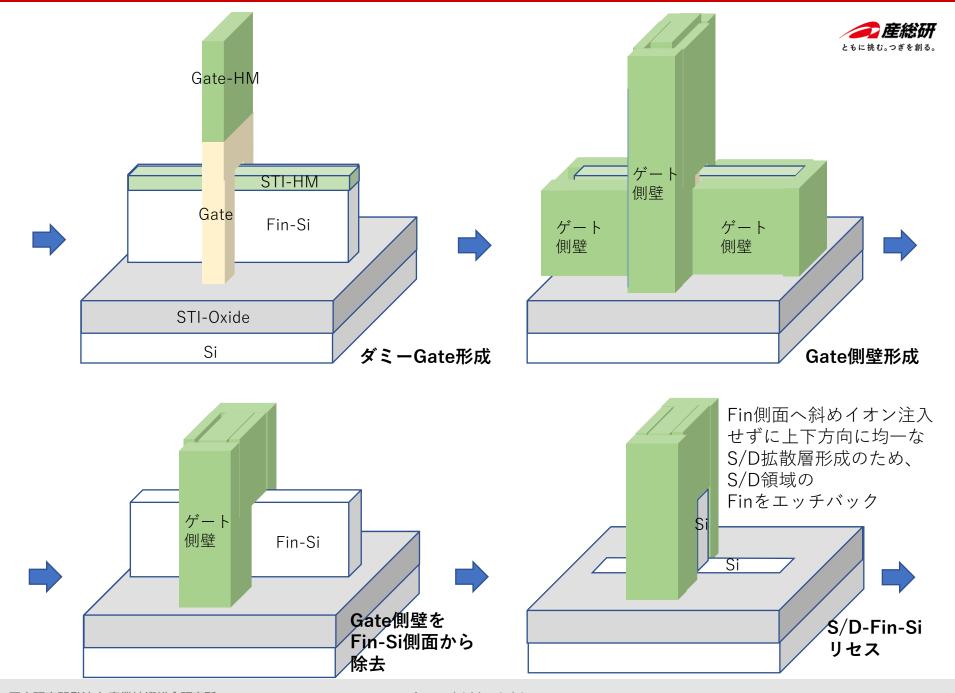

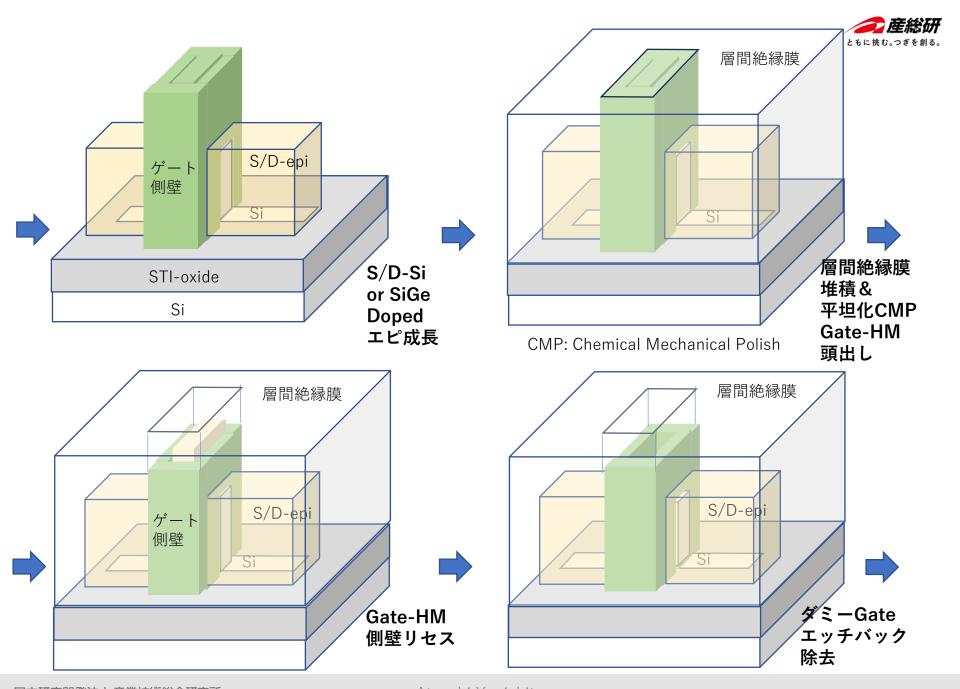

#### Fin-FETプロセスフロー鳥瞰図

14

- 1.トランジスタ構造の変遷と製造方法(基礎編)

- (1)新材料や新構造によるCMOSトランジスタの進展

- (2)Gate-First, Gate-Lastプロセス比較

- (3)PlanarFET, FinFET, GAAFET比較

- (4)Planar FETプロセス

- (5)FinFETプロセス

- (6) Nanosheet GAA(Gate-All-Around) FETプロセス

- Ⅱ. 学会動向(応用編)

- (1)GAAFET(IBM, 三星, GF)

- (2)CFET(imec,等)

- (3)2D材料(TSMC,imec,等)

- (4)裏面配線(Intel,三星,IBM, imec,等)

- Ⅲ. 将来展望(私見)

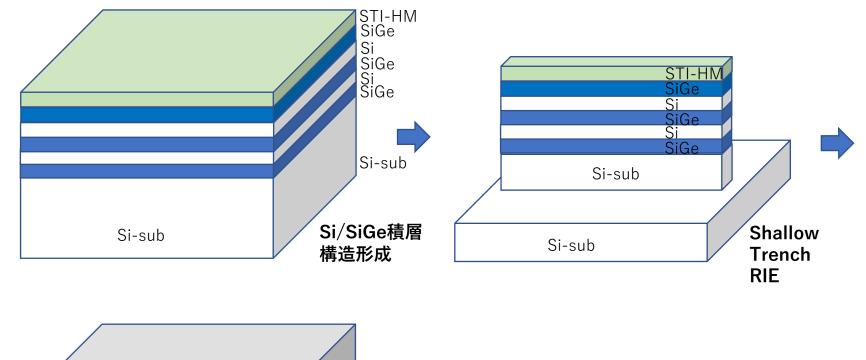

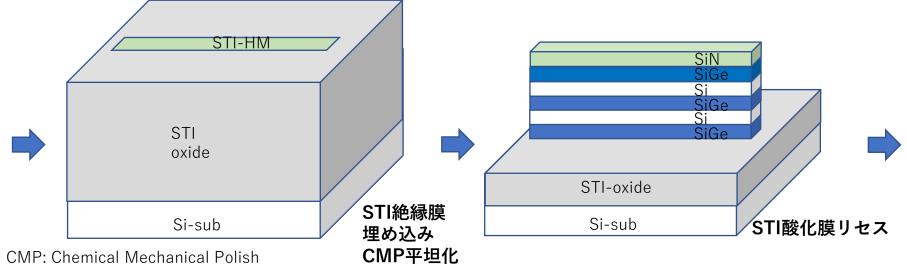

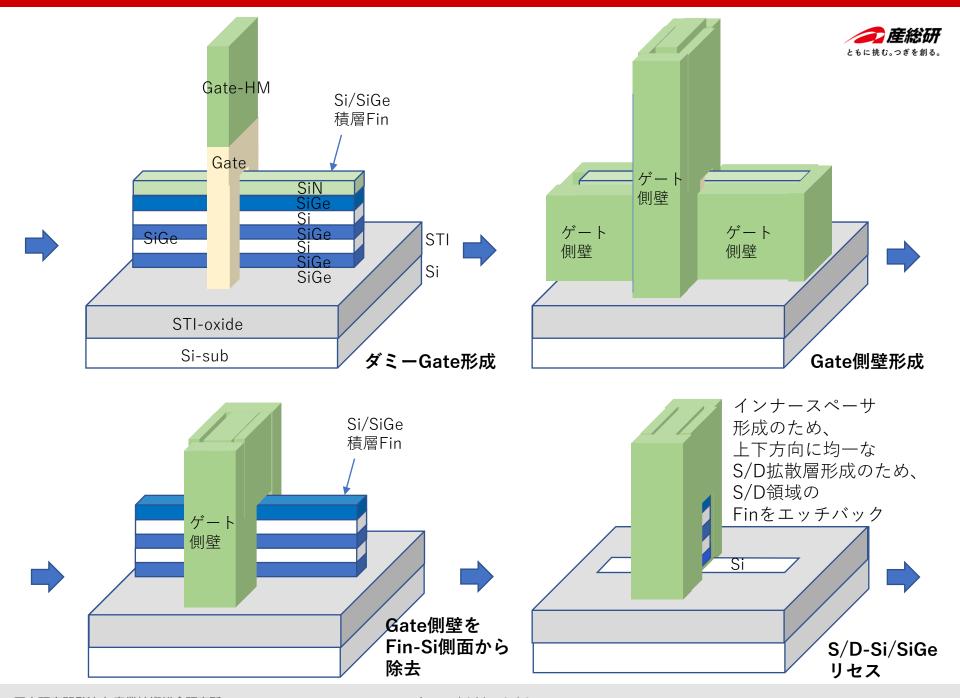

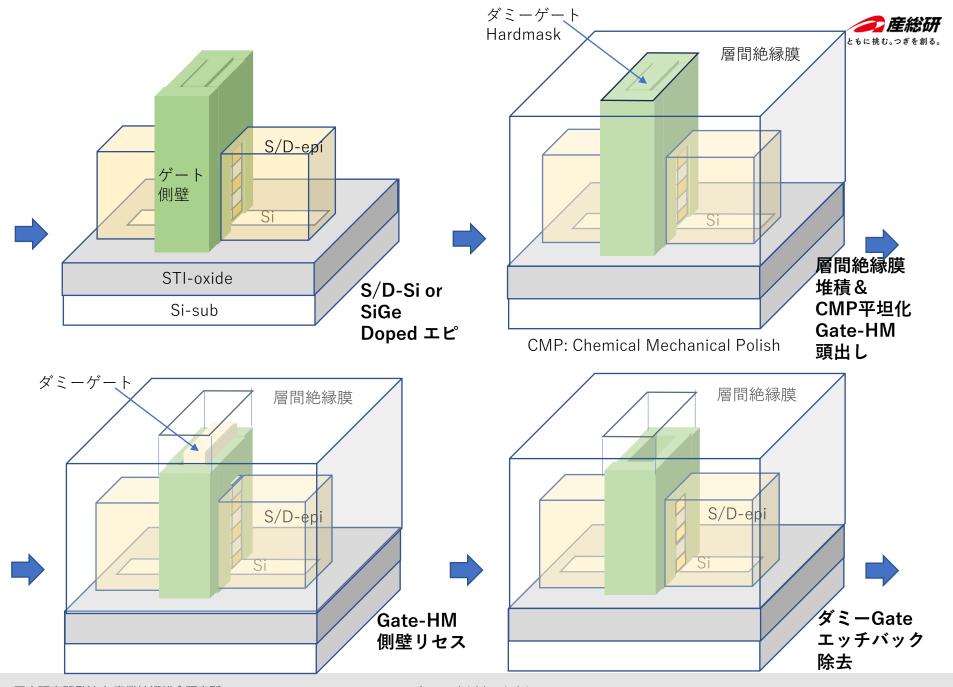

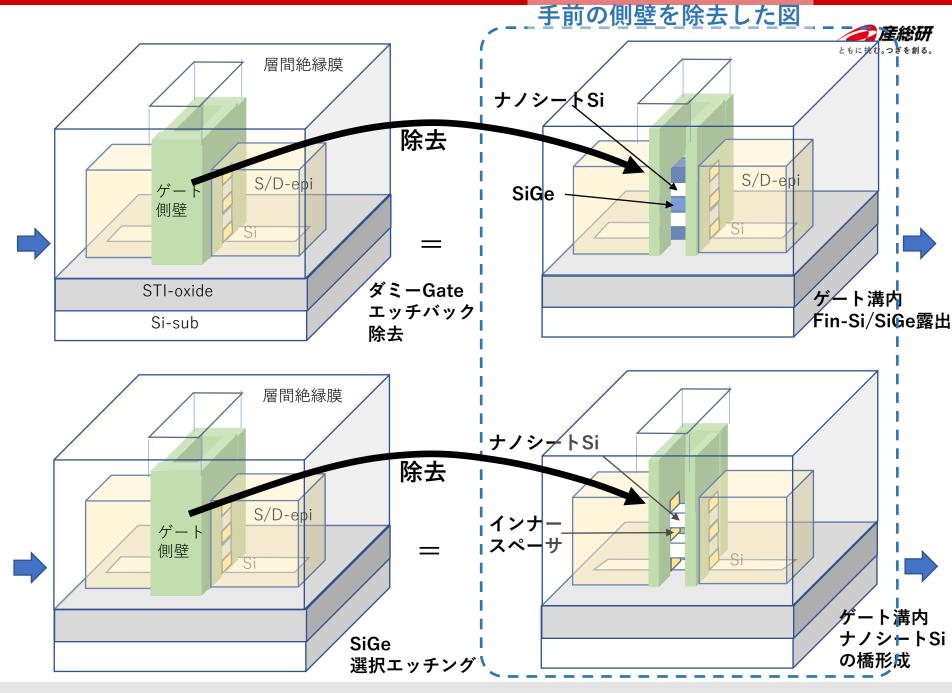

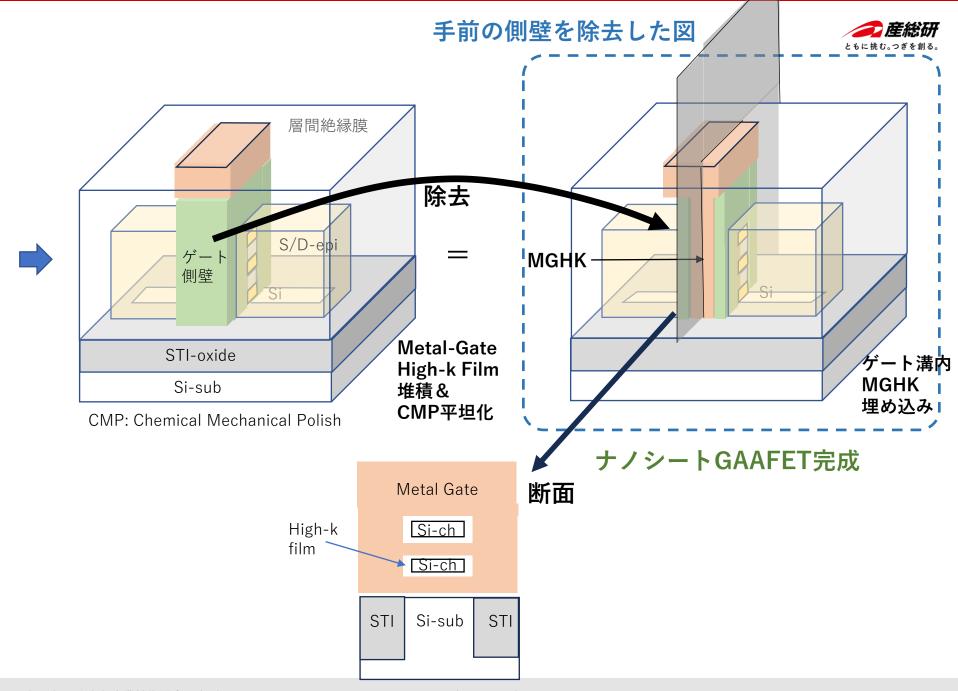

#### Nanosheet GAAFETプロセスフロー鳥瞰図

19

### トランジスタ構造の変遷のまとめ

・GateプロセスはPoly-Si-Gate/SiO2絶縁膜のGate-Firstから Metal Gate/High-kを用いた セルフアラインGate-Lastへ進化。

(電気的ゲート絶縁膜薄膜化しつつゲートリーク低減、 ゲート配線抵抗低減、Gate-S/Dセルフアライン、等のため)

・トランジスタ構造はPlanarFETからFinFET(立体化)、 ナノシートGAAFET(積層化)へと進化。

(ゲートのチャネル制御力を高め、微細化と高駆動力化のため)

・GAAFETはFinFETの発展形であり、両者の プロセスは類似する点が多い。